КАТЕГОРИИ:

АстрономияБиологияГеографияДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРиторикаСоциологияСпортСтроительствоТехнологияФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Защелкивание КМОП структур

Серьезная проблема проектирования КМОП схем заключается в том, чтобы избежать состояния, называемого защелкиванием. В этом состоянии в результате регенеративного срабатывания биполярных транзисторных структур между источником питания и землей схемы образуется фиксированная низкоомная проводящая цепь. Особенно важно избегать защелкивания в КМОП-структурах с малыми геометрическими размерами элементов, предназначенных для создания СБИС с высокой плотностью упаковки.

Чтобы объяснить суть явления защелкивания, рассмотрим КМОП структуру с карманами р-типа (рис. 5.4). На сечения отдельных МОП транзисторов этой структуры, показанные на рис. 5.4, наложены схемные изображения нежелательных, или паразитных, биполярных n-p-n и p-n-p-транзисторов. Эти транзисторы соединены друг с другом по перекрестной схеме, так что у них получается общий коллекторный переход. Из результирующей эквивалентной схемы биполярной структуры на рис. 4.4(??) видно, что в активном режиме смещения коллектор p-n-p-транзистора питает своим током базу n-p-n-транзистора, а коллектор n-p-n-транзистора – базу p-n-p-транзистора. Если эти биполярные транзисторы обладают хотя бы умеренными коэффициентами усиления по току, то в такой схеме включения оба они легко могут попасть в режим насыщения. В этом случае напряжение

Рисунок 5.4– Сечение КМОП-инвертора с карманом р-типа.

Паразитные биполярные p-n-p- и n-p-n-транзисторы показаны на рисунке вместе с соответствующими им подложечным резистором Rn и резистором кармана Rk.

В нормальных режимах работы КМОП-схем эмиттерные переходы обоих биполярных транзисторов смещены в обратном направлении, так что защелкивание КМОП-структур при этом невозможно. Для удачно спроектированной схемы может оказаться, что защелкивание невозможно ни в одном из возможных режимов ее работы. Чтобы понять, как в схеме может произойти защелкивание, обратимся к рис. 5.5, где воспроизведена пара биполярных транзисторов с перекрестными связями, а параллельно их коллекторным переходам подключены еще два схемных элемента – конденсатор (карман-подложка)Скп и источник тока I0 . Емкость конденсатора Скп значительно больше емкостей типовых коллекторных переходов транзисторов, так как этот конденсатор соответствует емкости перехода большой площади между карманом р-типа и подложкой ИС. В обычном режиме источник тока I0 моделирует только утечку перехода, поэтому его ток очень мал. Однако существует несколько механизмов, способных значительно увеличить ток I0 .

Рисунок 5.5- Эквивалентная схема, моделирующая эффект защелкивания в КМОП-структуре

В число возможных источников дополнительного тока через СкпI0 входят:

Облучение областей рентгентовским или гамма-излучением (энергия α-излучения недостаточна для включения тиристора)

Инжекция неосновных носителей. Если в процессе работы БИС через эквивалентные сопротивления RП RК протекает значительный ток, приводящий к вхождению одного из биполярных транзисторов тиристорной пары в режим насыщения, то какой-нибудь из эмиттеров начинает инжектировать носители, и тиристор включается. Аналогичный результат может иметь место и при включении питания UС (в случаеневысокой скорости нарастания напряжения) из-за влияния тока заряда емкости CН, а также при пиковых увеличениях (“бросках”) напряжения UС.

Инжекция из стоковых областей (управляющих электродов транзистора) в базовые области биполярных транзисторов. Этот эффект возможен при кратковременных пиковых превышениях выходного напряжения КМОП-схемы на 0,7В больше напряжения UС или на 0,7В наже UИ. Подобные броски выходных напряжений могут быть обусловлены как внешними импульсными помехами, так и паразитным влиянием ескости сток – затвор МОП-транзисторов быстродействующих базовых КМОП-схем.

Любой из этих источников тока может привести к включению одного или обоих биполярных транзисторов. Следовательно, защелкивание будет происходить, если пара биполярных транзисторов с перекрестными связями имеет достаточно высокое усиление, а источник питания Uc может отдавать достаточно большой ток.

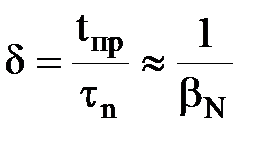

Простое выражение, в котором усиление прибора связано с условиями, допускающими защелкивание, можно получить, упростив схему на рис.5.5. Для этого исключим из нее I0 и (рис. 5.6). В таком режиме ток управления базой p-n-p-транзистора равен базовому току n-p-n-транзистора, умноженному на bn и на коэффициент деления между входным сопротивлением базы p-n-p-транзистора и сопротивлением подложки Rп включенным параллельно базе. Для малосигнального режима этот коэффициент равен bn Rп//(rpnp + Rп), где rpnp - величина, обратная  где

где  - крутизна,

- крутизна,  - коэффициент потерь. Аналогичное выражение для управляющего тока базы n-p-n-транзистора получается подстановкой вместо Rп сопротивления кармана Rк. Следовательно, полный коэффициент усиления по петле обратной связи Кос для этой транзисторной пары с перекрестными связями равен

- коэффициент потерь. Аналогичное выражение для управляющего тока базы n-p-n-транзистора получается подстановкой вместо Rп сопротивления кармана Rк. Следовательно, полный коэффициент усиления по петле обратной связи Кос для этой транзисторной пары с перекрестными связями равен

Кос =

| (5.1) |

В состоянии защелкивания коэффициент усиления по всей петле должен быть равен единице; и обратно, защелкивание невозможно, если этот коэффициент меньше единицы. Этот простой расчет показывает, что в схемах, не подверженных защелкиванию, необходимо максимально уменьшать коэффициенты усиления биполярных транзисторов bn и сопротивления Rп и Rк.

Уравнение (5.1) есть результат применения малосигнальной эквивалентной схемы биполярного транзистора и выражает условие, когда усиление схемы при переходном процессе достаточно для ее защелкивания. Если рассматривать статический случай и члены, связанные с действием резисторных делителей не играют роли, то это уравнение можно упростить и записать в виде

или или  , ,

| (5.2) |

а последнее соотношение можно свести к  , что является условием переключения тиристора в низкоомное состояние [ ]. Таким образом, показано, что в КМОП структуре, которую можно промоделировать, каки тиристор, с помощью 2-х биполярных транзисторов при условии

, что является условием переключения тиристора в низкоомное состояние [ ]. Таким образом, показано, что в КМОП структуре, которую можно промоделировать, каки тиристор, с помощью 2-х биполярных транзисторов при условии  образуется фиксированная низкоомная проводящая цепь. На этих основных принципах базируются практически все изученные на сегодняшний день способы проектирования КМОП схем, устойчивых к защелкиванию.

образуется фиксированная низкоомная проводящая цепь. На этих основных принципах базируются практически все изученные на сегодняшний день способы проектирования КМОП схем, устойчивых к защелкиванию.

Рисунок 5.6– Упрощенная модель для анализа коэффициентов усиления, требуемых для защелкивания КМОП структуры

Различают технологические, конструктивно-топологические и схемотехнологические меры по подавлению эффекта защелкивания. Из конструктивно-топологических мер следует указатть следующее: необходмо различать размещать контакты карманов и подложек так, чтобы сопротивления Rп и Rк стали как можно меньше; следует уменьшать коэффициенты усиления по току продольного p-n-pтранзистора за счет увеличения ширины его базы; располагать действующие в качестве коллекторов области так, чтобы токи включения и удержания тиристора повышались. В необходимом случае вокруг критических областей располагать кольцевые зоны защиты; минимизировать емкости сток – затвор. Применять кольцевые конструкции транзисторов со стоком, расположенным в центре.

К основным схемотехническим мерам можно отнести: применение специальных схем генераторов напряжений смещения подложки и изолирующих карманов, которые располагаются на кристалах БИС; использование диодов Шотки для предотвращения инжекций носителей заряда через стоковые p-n переходы при выбросах выходного напряжения КМОП-элементов; применение схем защиты входов и выходов, нечувствительных к тиристорному эффекту; включение на выходах и входах интегральных БИС диодов, имеющих пропускные напряжения ниже 0,7В; обеспечение небольшой скорости нарастания напряжения UС при включении (использование фильтрующих конденсаторов в цепи питания).

В настоящее время для создания карманов МОПТ разного типа проводимости используют фосфор и бор, с помощью которых формируют карманы на эпитаксиальных n-–пленке (рис. 5.7), стенки которых окисляют, а внутренность заполняют поликремнием. Эта технология стала доминирующей в транзисторах, выполненных по 0,25 микронной технологии и пришла на смену изоляции локальным окислением кремния (LOCOS). Это позволило минимизировать перекомпенсацию примеси в кармане и практически устранить эффект защелкивания.

Рисунок 5.7– Комплементарная пара транзисторов использованная в 0,25-мкм технологическом процессе.

В заключение отметим, что структуры ПТШ без электрода стока или с объединенными электродами стока и истока используются в качестве планарных диодов Шоттки. В последнем случае за счет снижения сопротивления базы RE =(R-1И+R-1c)-1достигается минимальное значение постоянной времени RБС, которая может составлять менее одной пикосекунды.

Дата добавления: 2014-11-13; просмотров: 1502; Мы поможем в написании вашей работы!; Нарушение авторских прав |