КАТЕГОРИИ:

АстрономияБиологияГеографияДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРиторикаСоциологияСпортСтроительствоТехнологияФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Использование операционного усилителя для построения инвертирующего усилителя.

Идеальный операционный усилитель Для уяснения принципов действия схем на ОУ и приближенного их анализа

оказывается полезным ввести понятие идеального операционного усилителя. Будем называть идеальным операционный усилитель, который имеет следующие свойства:

a) бесконечно большой дифференциальный коэффициент усиления по напряжению K U=Uвых /(U1 - U2) (у реальных ОУ от 1 тыс. до 100 млн.);

b) нулевое напряжение смещения нуля Uсм, т.е. при равенстве входных напряжений выходное напряжение равно нулю (у реальных ОУ Uсм , приведенное ко входу, находится в пределах от 5 мкВ до 50 мВ);

c) нулевые входные токи (у реальных ОУ от сотых долей пА до единиц мкА);

d) нулевое выходное сопротивление (у реальных маломощных ОУ от десятков Ом до единиц кОм);

e) коэффициент усиления синфазного сигнала равен нулю;

f) мгновенный отклик на изменение входных сигналов (у реальных ОУ время установления выходного напряжения от единиц наносекунд до сотен микросекунд).

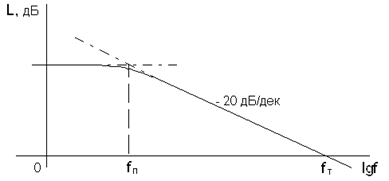

Как будет показано ниже, операционный усилитель, предназначенный для универсального применения, из соображений устойчивости должен иметь такую же частотную характеристику, что и фильтр нижних частот первого порядка (инерционное звено), причем это требование должно удовлетворяться по крайней мере вплоть до частоты единичного усиления fт, т.е. такой частоты, при которой |KU| =1.

В комплексной форме дифференциальный коэффициент усиления такого усилителя выражается формулой: Ки=Ки/1+j(f/fп) Здесь KU - дифференциальный коэффициент усиления ОУ на постоянном токе. Выше частоты fп, соответствующей границе полосы пропускания на уровне 3 дБ, модуль коэффициента усиления KU обратно пропорционален частоте. Таким образом, в этом диапазоне частот выполняется соотношение |KU| f = |KU| fп = fт

На частоте fт модуль дифференциального коэффициента усиления |KU| = 1. Как следует из последнего выражения, частота fт равна произведению коэффициента усиления на ширину полосы пропускания.

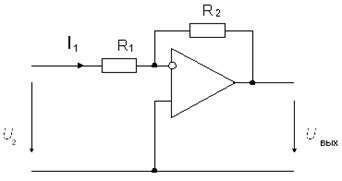

Инвертирующее включение

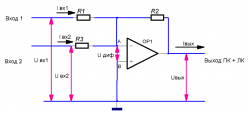

При инвертирующем включении неинвертирующий вход ОУ соединяется с общей шиной

(рис. 5).

Рис. 5. Инвертирующее включение ОУ К=U2/Uвых=-R2/R1

Таким образом, выходное напряжение усилителя в инвертирующем включении находится в противофазе по отношению ко входному. Коэффициент усиления входного сигнала по напряжению этой схемы в зависимости от соотношения сопротивлений резисторов может быть как больше, так и меньше единицы.

19 .Операционный усилитель – универсальный функциональный элемент, широко

используемый в современных схемах формирования и преобразования

информационных сигналов различного назначения как в аналоговой, так и в

цифровой технике.

Наименование «операционный усилитель» обусловлено тем, что, прежде всего

такие усилители получили применение для выполнения операций суммирования

сигналов, их дифференцирования, интегрирования, инвертирования и т. д.

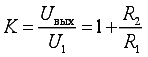

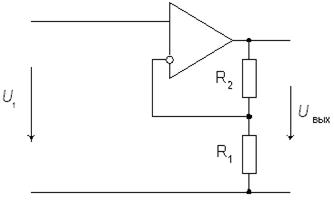

При неинвертирующем включении входной сигнал подается на неинвертирующий вход

ОУ, а на инвертирующий вход через делитель на резисторах R1 и R2

поступает сигнал с выхода усилителя (рис. 6). Здесь коэффициент усиления

схемы K найдем, положив в (6)

U2 = 0, R3 = 0, R4 бесконечно велико. Получим:

Рис. 6. Неинвертирующее включение ОУ

Как видно, здесь выходной сигнал синфазен входному. Коэффициент усиления по

напряжению не может быть меньше единицы. В предельном случае, если выход ОУ

накоротко соединен с инвертирующим входом, этот коэффициент равен единице.

Такие схемы называют неинвертирующими повторителями и изготавливают серийно в

виде отдельных интегральных микросхем, содержащих по нескольку усилителей в

одном корпусе. Входное сопротивление этой схемы в идеале - бесконечно. Ниже

будет показано, что у повторителя на реальном операционном усилителе это

сопротивление конечно, хотя и весьма велико.

20. Операционные усилители широко применяются в электронике, радиотехнике, в системах автоматического регулирования и управления.

На основе операционных усилителей выполняются типовые усилители с разными коэффициентами усиления, интеграторы, сумматоры и дифференцирующие звенья.

Операционный усилитель представляет собой усилитель постоянного тока с большим коэффициентом усиления по напряжению (десятки и сотни тысяч). Динамические свойства усилителя таковы, что он может быть замкнутым 100%-ной отрицательной обратной связью через резистор или конденсатор без потери устойчивости (без генерации) в замкнутом состоянии. сумматор на основе операционных усилителей.

Это обычный инвертирующий усилитель, охваченный обратной связью через резистор R2. Первое, что бросается в глаза — это подключение неинвертирующего входа к земляному проводу. То есть потенциал в точке «В» равен нулю. Следовательно, как известно из теории операционных усилителей, потенциал в точке «А» так же будет нулевым (равен потенциалу земли). Отсюда вывод:

Iвх = Uвх-Uдиф/R1; и Iвых = Uвых-Uдиф/R2.

Если принять во внимание, что входное сопротивление ОУ (между входами усилителя) бесконечно большое (стремиться к бесконечно большому значению), то входные и выходные токи будут стремиться к значению бесконечно малому. То есть к нулю. А при равности входного и выходного тока (или, говоря грубо, его отсутствии) формулы приведённые выше можно прировнять между собой:

Uвх/R1 = Uвых/R2 или Uвых/Uвх = — R2/R1, или Кус = — R2/R1.

Поскольку неинвертирующий вход соединён с землёй напряжение Uдиф будет бесконечно мало получаем, что потенциал инвертирующего входа так же стремиться к нулю. Отсюда имеем:

Iвх = Uвх/R1.

То есть, полное входное сопротивление устройства будет равно R1.

Наличие в точке «А» потенциала земли, позволяет подключать к схеме различное количество сопротивлений, работающих параллельно R1, что превращает инвертирующий усилитель в прекрасный сумматор.

По скольку точка «А», напомню, имеет потенциал земли (и токи стремятся к нулю), то имеем:

Uвх1/R1+Uвх2/R3 = 0

Отсюда:

Uвых = — (Uвх1 + Uвх2)

Резисторы не обязательно должны быть одинаковыми. Если они различны, то на выходе получим взвешенную сумму. Это явление используют, например, в микшерах, когда необходимо суммировать несколько сигналов от различных источниках и имеющих различные уровни. Количество смешиваемых источников, также, может быть различно.

21 Алгебра логики (булева алгебра) – это раздел математики, возникший в XIX веке благодаря усилиям английского математика Дж. Буля. Поначалу булева алгебра не имела никакого практического значения. Однако уже в XX веке ее положения нашли применение в описании функционирования и разработке различных электронных схем. Законы и аппарат алгебры логики стал использоваться при проектировании различных частей компьютеров (память, процессор).

Логические операции удобно описывать так называемыми таблицами истинности, в которых отражают результаты вычислений сложных высказываний при различных значениях исходных простых высказываний. Простые высказывания обозначаются переменными (например, A и B)

Логические элементы — устройства, предназначенные для обработки информации в цифровой форме (последовательности сигналов высокого — «1» и низкого — «0» уровней в двоичной логике, последовательность «0», «1» и «2» в троичной логике, последовательности «0», «1», «2», «3», «4», «5», «6», «7», «8» и «9» в десятичной логике). Физически логические элементы могут быть выполнены механическими, электромеханическими (на электромагнитных реле), электронными (на диодах и транзисторах), пневматическими, гидравлическими, оптическими и др.

С развитием электротехники от механических логических элементов перешли к электромеханическим логическим элементам (на электромагнитных реле), а затем к электронным логическим элементам на электронных лампах, позже — на транзисторах. После доказательства в 1946 г. теоремы Джона фон Неймана об экономичности показательных позиционных систем счисления стало известно о преимуществах двоичной и троичной систем счисления по сравнению с десятичной системой счисления. От десятичных логических элементов перешли к двоичным логическим элементам. Двоичность и троичность позволяет значительно сократить количество операций и элементов, выполняющих эту обработку, по сравнению с десятичными логическими элементами.

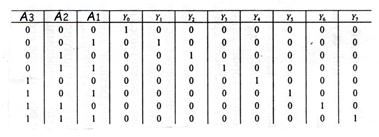

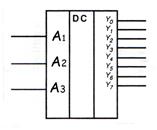

22. Дешифратором называется комбинационное устройство, преобразующее n — разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. Функции дешифратора показан на рисунке:

Условное графическое обозначение (УГО) и таблица истинности дешифратора приведены на рисунке:

Активным всегда являются только один выход. Легко заметить, что активируется тот выход, адрес которого установлен на входах. Дешифраторы широко используются в цифровой аппаратуре.

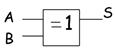

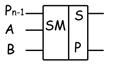

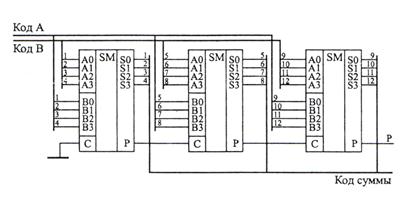

23. Сумматоры — это комбинационные устройства, предназначенные для сложения двух входных двоичных кодов. Например, арифметическая сумма кодов 0111 (число 7) и 0101 (число 5) равна 1100 (число 12). Арифметическая сумма кодов 1101 (число 13) и 0110 (число 6) равна 10011 (число 19), т. е. сумма двух двоичных чисел с числом разрядов n может иметь результат с числом разрядов n + 1. Этот дополнительный (старший) разряд называется выходом переноса (Р). На схемах сумматоры обозначаются буквами SM. Микросхемы сумматоров кодируются буквами ИМ.

Рассмотрим таблицу истинности сложения двух одноразрядных двоичных чисел без учёта переноса:

| A | B | S |

Запишем логическую функцию:

S =AB+AB

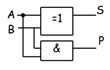

Устройство, реализующее эту функцию, называется " исключающее ИЛИ":

Схема не информирует о бите переноса.

Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значение входных чисел А и В, значение результата суммирования S и значения переноса в старший разряд Р:

| A | B | P | S |

Работа устройства, реализующего таблицу истинности, описывается следующими уравнениями:

S = AB+ABи Р = АВ

Устройство, реализующего таблицу истинности, содержит " исключающие ИЛИ" и конъюнктор " И"

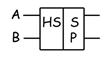

Это устройство называется полусумматором и изображается в виде:

Устройства называются полусумматором, т. к. имеет только два входа и не воспринимается сигнал переноса от других микросхем. Он используется только в младшем разряде.

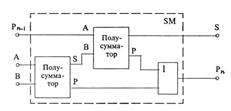

Рассмотрим сложение двух одноразрядных двоичных чисел с учётом бита переноса от других микросхем:

Работа устройства, реализующего таблицу истинности, описывается следующими уравнениями:

S=ABPn-1+ABPn-1+ABPn-1+ABPn-1

Pn=ABPn-1+ABPn-1+ABPn-1+ABPn-1

Устройство, реализующие таблицу, содержит два полусумматора и дизъюнктор " ИЛИ":

Это устройство называется одноразрядным сумматором и имеет следующее условное графическое обозначение:

Вход С (вход расширения) для объединения нескольких сумматоров с целью увеличения разрядности:

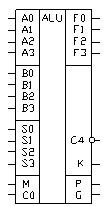

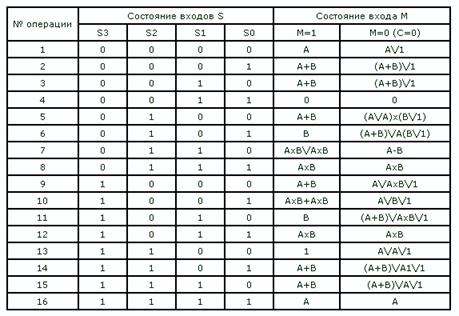

24.Арифметико-логическое устройство (АЛУ) - это многофункциональное устройство, которое выполняет над входными числами различные арифметические и логические операции. Схемотехнически АЛУ представляется вот так:

АЛУ имеет входы чисел А0-А3 и В0-В3, входы управления S0-S3, М, вход переноса С0, выход результата F0-F3, выход переноса С4, выход равенства кодов К, выходы Р и G для схемы быстрого переноса. Работа АЛУ поясняется таблицей функционирования, изображенной ниже. Вход М определяет вид выполняемых операций (при М=1 над А и В выполняется 16 лог.операций, при М=0 выполняются арифметические операции). Знаком \/ обозначается лог. сложение, арифметическое сложение обозначается плюсиком (+), умножение (только логическое) - знаком "х", А1 - число А, сдвинутое на один разряд вправо.

АЛУ может выполнять следующие операции:

-Арифметическое суммирование чисел (при М=0 операция №10).

-Арифметическое вычитание чисел (при М=0 операция №7).

-Сравнение чисел - операция №7 при С0=1. Если А=В, то К=1, если A>B, то С4=0, если A<B, то С4=1.

-Формирование модуля числа А. При М=1 на входы S3-S0 параллельно подается знак числа А равный 1 при положительном числе А. Если А отрицательно - 0. Для S=1 выполняется 16-я операция, S=0 - 1-я. Также для числа В (11-я и 6-я операции соответственно), но нужно иметь знак и его инверсию.

-Мультиплексирование чисел А и В. При М=1 и 16-й операции на выход поступает число А, 11-я операция - число В. 1-я и 6-я операции выполняют мультиплексирование с инверсией.

-Увеличение числа А в 1,5 раза - 13 операция.

Наращивание разрядности АЛУ делается также, как и в сумматорах, т. е. выход переноса С4 АЛУ младших разрядов подключается к входу переноса С0 АЛУ старших разрядов. Но при большом числе разрядов время выполнения операций увеличивается из-за большого числа переносов из разряда в разряд. Для ускорения этого процесса используются специальные микросхемы, которые зовут схемами ускоренного переноса (555ИП4, 564ИП4). Одна такая микросхема обслуживает до 4-х АЛУ. Выходы G и Р АЛУ втыкаем на аналогичные входы G и Р схемы ускоренного переноса, а выходы переноса последней втыкаем на входы переноса АЛУ. Вход переноса АЛУ младшего разряда подключается к входу переноса микросхемы переноса. При этом объединяются входы М всех АЛУ. Получается 16-ти разрядное АЛУ.

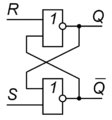

- Основные понятия о триггерах как последовательностных устройствах. Входы и выходы триггера, синхронные и асинхронные триггеры, триггеры со статическим и с динамическим управлением.

Триггеры относятся к цифровым автоматам. В отличие от комбинационных схем состояние на выходе триггера в данный момент времени определяется не только состояниями на входах триггера в этот же момент времени, но и предыдущим состоянием триггера. Цифровые автоматы, к которым относятся триггеры, иногда называют последовательными схемами.

Триггеры имеют два устойчивых состояния. Эти состояния определяются по логическим уровням на выходах триггера. Триггер снабжается двумя выходами: прямым Q и инверсным Q. Состояние триггера определяет логический уровень на выходе Q. Триггеры могут иметь входы различного типа:

R (от англ. RESET) – раздельный вход установки в состояние 0;

S (от англ. SET) – раздельный вход установки в состояние 1;

К – вход установки универсального триггера в состояние 0;

J – вход установки универсального триггера в состояние 1;

V – вход разрешения;

С – синхронизирующий вход;

D – информационный вход;

Т – счетный вход и др.

Обычно название триггера дают по имеющимся у него входам: RS-триггер, JK-триггер, D-триггер и др.

По способу записи информации триггеры подразделяются на асинхронные и синхронные. В асинхронных триггерах состояние на выходе изменяется сразу же после изменения сигнала на информационных входах. В синхронных триггерах для передачи сигнала с информационных входов на выходы требуется специальный синхронизирующий импульс. Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигнала с информационных входов на выходы осуществляется по фронту или по спаду синхронизирующего импульса.

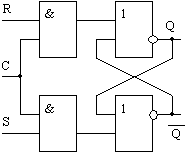

- Схема асинхронного RS-триггера на логических элементах 2ИЛИ-НЕ и её функционирование.

RS-триггер с прямыми входами можно получить, имея в наличии два логических элемента 2ИЛИ-НЕ. По отношению к логическим элементам триггер симметричен. По этой причине не имеет принципиального значения, выход какого из элементов считать прямым выходом триггера. Допустим, что прямым выходом триггера является верхний вывод. Определим, какой из входов триггера является входом R, а какой – входом S. Так как активным логическим уровнем для элементов ИЛИ-НЕ является уровень логической единицы, т.е. если на входе элемента 2ИЛИ-НЕ действует логическая «1», то на выходе будет «0». Зная, что вход R – это вход установки триггера в нулевое состояние, приходим к выводу, что входом R в данном случае будет верхний вход RS-триггера.

RS-триггер с прямыми входами можно получить, имея в наличии два логических элемента 2ИЛИ-НЕ. По отношению к логическим элементам триггер симметричен. По этой причине не имеет принципиального значения, выход какого из элементов считать прямым выходом триггера. Допустим, что прямым выходом триггера является верхний вывод. Определим, какой из входов триггера является входом R, а какой – входом S. Так как активным логическим уровнем для элементов ИЛИ-НЕ является уровень логической единицы, т.е. если на входе элемента 2ИЛИ-НЕ действует логическая «1», то на выходе будет «0». Зная, что вход R – это вход установки триггера в нулевое состояние, приходим к выводу, что входом R в данном случае будет верхний вход RS-триггера.

В асинхронных триггерах состояние на выходе изменяется в момент поступления сигналов на информационные входы.

- Схема синхронного RS-триггера на логических элементах 2ИЛИ-НЕ и её функционирование.

При С = 0 на входах R, S асинхронного триггера на элементах 1 и 1 действуют сигналы логического нуля (логический нуль является пассивным логическим уровнем для логических элементов 2ИЛИ-НЕ), поэтому при любых комбинациях сигналов на входах R, S синхронного RS-триггера состояние триггера не меняется. При С = 1 рассмотренный синхронный RS-триггер работает точно так же, как асинхронный RS-триггер с прямыми входами. Этот RS-триггер относится к триггерам со статическим управлением.

В синхронных триггерах для передачи сигнала с информационных входов на выход требуется специальный синхронизирующий импульс.

Дата добавления: 2015-04-16; просмотров: 445; Мы поможем в написании вашей работы!; Нарушение авторских прав |