КАТЕГОРИИ:

АстрономияБиологияГеографияДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРиторикаСоциологияСпортСтроительствоТехнологияФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Модели организации виртуальной памяти.

1. База и Придел.(простейшая, линейная).

Снабдим процессор 2мя регистрами спец. назначения База и Придел, можно считать, что в привилигирован. режиме знач-я этих регистров игнорируются. При работе ЦП в ограничен. режиме при выполенении любой ком-ды, ЦП к любому заданному в программе исполнит. адресу прибавляет значение Баз. При этом получается физич. адрес. На аппаратн. уровне производится проверка не превышает ли полученное значение предела, если превыш., то прерывание.

Модификация базы и придела в ограничен. режиме запрещена.

При перемещении задачи в др. место памяти копируется адресн. пространство по новым адресам соотв-но изменяется знач-е Базы и Придела.

В такой модели идеально решена проблема памяти и адаптации к адресам. Проблема объема памяти и фрагментации может решаться, но довольно сложно. Проблема дублир-я не решена вообще.

2. Сегментная адресация памяти.

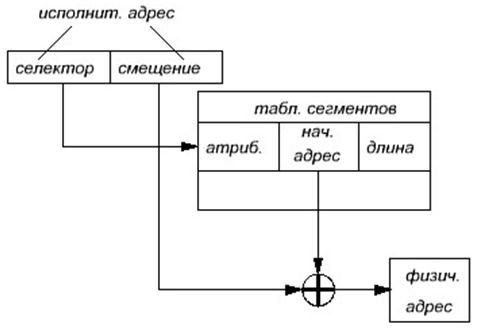

Сегмент- область физич. памяти, имеющ. начало(аналогично Базе) и длину(аналогично Приделу). Отличие: позволено задаче иметь неск. сегментов. Такая схема модели затронет процессор и все ПО. Наиболее видимое измен-е: в исполнит. адресе появл. селектор сегмента под него отводят неск. старших бит адреса или использует отдельн. спец-но предназначен. регистр процессора. Селектор сод-т номер сегмента в таблице дискрипторов сегмента. Структура инф-ции в таблице для каждого сегмента след.: физ. адрес начала сегмента, его длина и некот. служебн. пар-ры и флаги.

Физич. адрес формер-ся сложением адреса начала сегмента из табл. дискрипторов и смещения взятого из исполнит. адреса.

Возможность иметь неск. сегментов для 1ой задачи позволяет сделать некот. сегмент общим => можно решить проблему дублир-я. Пр. задача с неск. большими таблицами, чтобы не пересчитывать все адреса можно для каждой таблицы выделить свой сегмент.

Разработчики архитектур организуют процесс хранения инф-ции об используемых сегментах непосредственно в процессоре.

3. Страничная организация памяти.

Каждая задача имеет свое пространство вирт. адресов и свои табл. перевода их в физич. Разделим физич. память на кадры frame фиксир. размера.

Каждая задача имеет свое пространство вирт. адресов и свои табл. перевода их в физич. Разделим физич. память на кадры frame фиксир. размера.

Пространство вирт. адресов разбивается на страницы того же размера, что и кадры.

Если процессор имеет 32 битн. адреса объем физич. памяти 512 Мбайт= 212 Б.

фреймов 217 кадров.

Вирт. адресн. пр-во тогда делится тоже на страницы по 4 Кб.

Нужно некот. образом для каждой задачи сопоставить некот. страницы номера физич. кадров. Обычно отображение страниц на физич. кадры осущ-ся через таблицу страниц. Таблица, принадлежащая активной задаче, для каждой страницы таблицы есть запись с номером кадра и служебн. атрибуты. В число атрибутов входит признак присутствия таблицы в ОП. Сущ. проблема выбора размера страницы.

Чем больше страница, тем больше памяти пропадает впустую, чем меньше страница, тем больше строк в таблице страниц.

Чем больше страница, тем больше памяти пропадает впустую, чем меньше страница, тем больше строк в таблице страниц.

На Intel 4Кб, 2 Мб страниц. Каждая строка в табл. страниц занимает 4Б. Кол-во страниц по 4 Кб, если 4 Гб памяти =220.

Многоуровневые страницы таблицы в этом случае №страницы делится на группы битов, задающих номер строки в таблицах соотв. уровню. Таблица 1ого уровня сод-т адреса таблиц 2ого и т.д. уровня. Таблица 2ого и т.д. уровня номера физич. кадров.

Многоуровневые страницы таблицы в этом случае №страницы делится на группы битов, задающих номер строки в таблицах соотв. уровню. Таблица 1ого уровня сод-т адреса таблиц 2ого и т.д. уровня. Таблица 2ого и т.д. уровня номера физич. кадров.

Обычно идет 2 уровня для 32 бита вых. структур и 3 уровня для 64 бит. Таблицы уровня добавл. по мере необх-ти.

Для 32 битн. адресов, если размер страницы 4 Кб, таблицы обоих уровней могут сод-ть 10 бит – вирт. адрес на каждую таблицу. Т.е. каждая страница займет 1 кадр.

«-» будет пропадать память на последн. страницы и довольно большой объем служебн. инф-ции.

Встраивают в процессор спец. уст-во назыв. ассоциативной памятью. Уст-во представл. собой табл. из 2х полей: №вирт. страницы и инф-ция о соотв-щем кадре. Электрон. схема устроена так, что запрос к ней осущ-ся не по номеру строки в табл., а по знач-ю 1ого поля, т.е. по ключу.

Инф-ция об отображаемой странице локальна для каждой задачи. Каждая страница дополняет ассоциативн. память заново. Если управление ассоц. памятью на нов. системе, то все запросы на нов. заполнение через прерывание.

Сегментно – страничная организация памяти.

В этой модеи задача имеет неск. сегментов причем, каждый из сегментов представл. собой самостоятельн. вирт. адресн. пр-во, поделен. на страницы.

«-» сложность.

С ней практически не работают сегодня.

Дата добавления: 2015-01-14; просмотров: 272; Мы поможем в написании вашей работы!; Нарушение авторских прав |