КАТЕГОРИИ:

АстрономияБиологияГеографияДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРиторикаСоциологияСпортСтроительствоТехнологияФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Регистр флагов внешних прерыван ий

Возникновение внешних прерываний индицируется установкой флагов регистра флагов внешних прерываний (GIFR - General Interrupt Flag Register).

Возникновение внешних прерываний индицируется установкой флагов регистра флагов внешних прерываний (GIFR - General Interrupt Flag Register).

| Адрес: $38 ($58) | ||||||||||||

| GIFRБиты | INTF1 | INTF0 | INTF2 | - | - | - | - | - | ||||

| Чтение/запись | R/W | R/W | R/W | R | R | R | R | R | ||||

| Начальное состояние |

· Bits 7 – 5 – INTF1 – INTF2: External Interrupt 1 – 2 Flags – флаги внешних прерываний 1 – 2.

При поступлении запроса на прерывание на какой-либо из выводов INT0 – INT2, будет установлен в состояние лог. 1 соответствующий флаг прерывания INTF0 – INTF2. Если бит I регистра статуса и соответствующий

бит разрешения INT0– INT2 в общем регистре управления прерываниями будут установлены, то MК перейдет на начало вектора прерывания. По завершении подпрограммы прерывания флаг очищается. Кроме того, его можно очистить, записав в него лог. 1.

· Bits 4 – 0 - Res: Reserved Bits – зарезервированные биты.

Эти биты зарезервированы и при считывании всегда покажут состояние лог. 0.

Дополнение:

Описание работы таймера/счётчика 0.

Прерывания от TC0

Таймер/счётчик 0 (TC0) представляет из себя 8-битный модуль, содержащий 3 регистра. В регистре TCNT0 происходит счёт импульсов. Регистр доступен как для чтения, так и для записи, т.е. можно задать некое начальное значение и ТС0 продолжит счёт от этого значения. Счёт идёт на увеличение. Скорость и режимы счёта можно задать с регистра TCCR0. Общий вид регистра TCCR0:

Тактовая частота процессора подаётся на вход схемы деления частоты ТС0. Делённая частота попадает на счётную схему. Режимы деления задаются в трёх младших битах регистра TCCR0:

Таким образом, если в эти три бита записаны 000, то ТС0 остановлен. Если 001, то ТС0 считает импульсы частоты процессора. И если один так процессора длится 1 мс, то в в TCNT0 значение будет увеличиваться каждую 1 мс. Если записано 101, то схема предделения будет тактовую частоту процессора делить на 1024, и один раз за 1024 такта процессора ТС0 будет увеличивать значение в TCNT0. External Clock Source - режим счёта внешних импульсов, поступающих на вывод T0.

Остальные биты позволяют устанавливать такие режимы счётчика, при которых он будет своё состояние показывать на выводe OC0.

Регистр OCR0 служит для задания значения, при достижении которого в режиме счёта, ТС0 генерирует прерывание.

Обработка прерываний от TC0

ТС0 при переполнении значения TCNT0 посылает процессору сигнал Timer/Counter 0 Overflow. Также процессору посылается сигнал Timer/Counter 0 Compare Match при совпадении значений в регистрах TCNT0 и OCR0. Реакция процессора на эти сигналы (вызов соответствующих прерываний) зависит от значения

регистров TIMSK и флага I в Status регистре процессора.

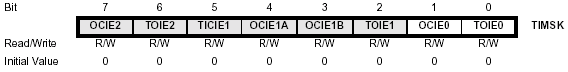

Для задания реакции на события TC0 в регистре TIMSK служат два бита:

Бит 0 - TOIE0 - Когда этот бит установлен в 1 и разрешены прерывания, процессор реагирует на сигнал переполнения ТС0 и вызывает прерывание по вектору $012 (OVF0addr).

Бит 1 - OCIE0 - Когда этот бит установлен в 1 и разрешены прерывания, процессор реагирует вызовом прерывания по вектору $026 (OC0addr) на событие совпадения счёта с константой в регистре OCR0.

Дата добавления: 2015-01-19; просмотров: 286; Мы поможем в написании вашей работы!; Нарушение авторских прав |