КАТЕГОРИИ:

АстрономияБиологияГеографияДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРиторикаСоциологияСпортСтроительствоТехнологияФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Функции процессора. Системная магистраль, назначение шин. Схема подключения процессора, основные выводы микросхемы процессора.

основные функции любого процессора следующие:

1)выборка (чтение) выполняемых команд;

2)ввод (чтение) данных из памяти или УВВ;

3)вывод (запись) данных в память или УВВ;

4)обработка данных (операндов), в том числе арифметические операции над ними;

5)адресация памяти, т. е. задание адреса памяти, с которым будет производиться обмен;

6)обработка прерываний и режима прямого доступа к памяти (ПДП).

Важнейшая характеристика процессора-разрядность.Разрядность ШД-скорость работы системы.Разрядность ША-допустимая сложность системы.Кол-во линий управления определяет разнообразие режимов обмена и эффективность обмена процессора с другими устройствами системы.

Магистраль (системная шина) включает в себя три многоразрядные шины:шину данных, шину адреса,шину управления.

Шина данных служит для пересылки данных между ЦП и памятью или ЦП и устройствами ввода/вывода.Шина адреса .Выбор устройства или ячейки памяти, куда пересылаются или откуда считываются данные по шине данных, производит процессор.Каждое устройство или ячейка оперативной памяти имеет свой адрес. Адрес передается по адресной шине, причем сигналы по ней передаются в одном направлении - от процессора к оперативной памяти и устройствам (однонаправленная шина).По шине управления передаются управляющие сигналы, определяющие характер обмена информацией по магистрали и предназначенные памяти и устройствам ввода/вывода.

Микросхема процессора обязательно имеет выводы трех шин: шины адреса, шины данных и шины управления.CLK-подключение внешнего тактового сигнала и тактового резонатора (быстродействие CPU). RESET-сигнал начального сброса. Для подключения CPU к магистрали используют буферные микросхемы, обеспечивающие, если необходимо, демультиплексирвоание сигналов и электрическое буферирование сигналов магистрали. Буферные микросхемы согласуют протоколы шин процессора и магистрали если они не совпадают.

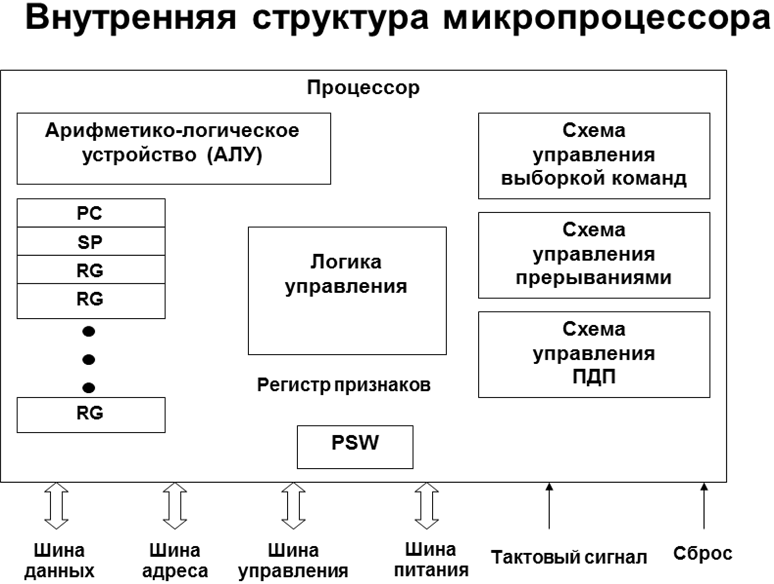

Внутренняя структура микропроцессора. Схема управления выборкой команд, АЛУ, регистры процессора, схема управления прерываниями, схема управления прямым доступом к памяти, логика управления.

Схема управления выборкой команд выполняет чтение команд из памяти и их дешифрацию.

Арифметико-логическое устройство (или АЛУ, ALU) предназначено для обработки информации в соответствии с полученной процессором командой. Быстродействие АЛУ во многом определяет производительность процессора. Причем важна не только частота тактового сигнала, которым тактируется АЛУ, но и количество тактов, необходимое для выполнения той или иной команды.

Для повышения производительности разработчики стремятся довести время выполнения команды до одного такта, а также обеспечить работу АЛУ на возможно более высокой частоте. Другой путь повышения производительности процессора — использование нескольких параллельно работающих АЛУ.

Регистры процессора представляют собой по сути ячейки очень быстрой памяти и служат для временного хранения различных кодов: данных, адресов, служебных кодов. Операции с этими кодами выполняются предельно быстро, поэтому, в общем случае, чем больше внутренних регистров, тем лучше. Кроме того, на быстродействие процессора сильно влияет разрядность регистров. Именно разрядность регистров и АЛУ называется внутренней разрядностью процессора, которая может не совпадать с внешней разрядностью.

По отношению к назначению внутренних регистров существует два основных подхода. Первого придерживается, например, компания Intel, которая каждому регистру отводит строго определенную функцию. С одной стороны, это упрощает организацию процессора и уменьшает время выполнения команды, но с другой — снижает гибкость, а иногда и замедляет работу программы. Второй подход состоит в том, чтобы все (или почти все)регистры сделать равноправными, как , например, в 16-разрядных процессорах Т-11 фирмы DEC. При этом достигается высокая гибкость, но необходимо усложнение структуры процессора.PSW-содержит информацию о выполнении пред-й команды.

Среди общих регистров имеются регистры специального назначения: указатель стека SP (Stack Pointer), счетчик команд PC (Program Counter)

Схема управления прерываниями обрабатывает поступающий на процессор запрос прерывания, определяет адрес начала программы обработки прерывания (адрес вектора прерывания), обеспечивает переход к этой программе после выполнения текущей команды и сохранения в памяти (в стеке) текущего состояния регистров процессора. По окончании программы обработки прерывания процессор возвращается к прерванной программе с восстановленными из памяти (изстека) значениями внутренних регистров.

Схема управления прямым доступом к памяти служит для временного отключения процессора от внешних шин и приостановки работы процессора на время предоставления прямого доступа запросившему его устройству.

Логика управления организует взаимодействие всех узлов процессора, перенаправляет данные, синхронизирует работу процессора с внешними сигналами, а также реализует процедуры ввода и вывода информации.

Дата добавления: 2015-04-18; просмотров: 1068; Мы поможем в написании вашей работы!; Нарушение авторских прав |