КАТЕГОРИИ:

АстрономияБиологияГеографияДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРиторикаСоциологияСпортСтроительствоТехнологияФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Использование схем с тристабильными выходами в цифровых устройствах.

Тристабильная схема отличается тем, что ее выход может иметь три различных состояния. С TTL — схемами она может работать как обычная схема, имеющая относительно низкие выходные сопротивления в состояниях логический 0 и логическая 1, когда на управляющий вход схемы подан высокий потенциал. Треть состояние, характеризующиеся очень высоким выходным сопротивлением, имеет место при подаче на управляющий вход низкого потенциала. Когда управляющий вход имеет низкий потенциал (заземлен), управляющий ток уходит, что вызывает появление третьего состояния. Если управляющий вход имеет высокий потенциал, то схема работает как обычный инвертор. Таблица истинности иллюстрирует работу этой схемы.

| Данные | Управление | Выход |

| Высокий Z | ||

| Высокий Z | ||

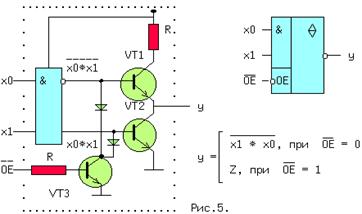

Наряду с двумя логическими состояниями существует третье технологическое состояние, когда выход элемента отключается от внутренней схемы. При этом сопротивление между выходом и "землей" становится очень большим и выход микросхемы не оказывает никакого влияния на подключенные к нему выходы других микросхем. Выходы нескольких таких элементов также могут соединяться вместе. Такое включение , применяется там, где несколько источников сигналов по очереди подключаются к входам одного или нескольких приемников, не мешая друг другу. Третье состояние называют также высокоимпедансным или Z - состоянием. Схема И-НЕ с Z-состоянием выхода приведена на рис.5. слева, а ее условное обозначение - справа.

Если сигнал ~OE=0, транзистор VT3 закрыт и включенные встречно диоды не оказывают влияния на логические выходы элемента И. Напряжения на базах транзисторов VT1 и VT2 находятся в противофазе и, если x0*x1=1, то верхний транзистор закрыт, а нижний открыт. Потенциал коллектора VT2 примерно равен нулю и следовательно y=0. При других значениях x0 и x1 нижний транзистор заперт, а верхний открыт и на выходе схемы - высокий уровень, т.е. при ~OE=0 схема работает как обычный элемент И-НЕ. Картина существенно изменится при ~OE=1. Транзистор VT3 откроется до насыщения и на базах транзисторов VT1 и VT2 потенциал опустится примерно до нуля, запирая их. Выход "y" окажется отключенным от внутренней логической схемы

Дата добавления: 2015-04-21; просмотров: 415; Мы поможем в написании вашей работы!; Нарушение авторских прав |