КАТЕГОРИИ:

АстрономияБиологияГеографияДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРиторикаСоциологияСпортСтроительствоТехнологияФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Порядок виконання команд

Команди зберігаються в основній пам'яті комп'ютера за відповідними адресами. Для того, щоб виконати команду та здійснити обробку даних, команду та дані потрібно зчитати з основної пам'яті та записати до відповідних регістрів процесора. Комп'ютер виконує кожну команду як послідовність простих операцій:

1.Вибірка чергової команди із основної пам'яті.

2.Визначення типу вибраної команди, тобто її дешифрування.

3.Визначення адрес даних, необхідних для виконання цієї команди.

4.Виконання операцій пересилання даних (зчитування даних із пам'яті в регістри процесора).

5.Виконання операції відповідно до її коду в полі коду операції команди.

6.Визначення адрес, за якими запам'ятовуються результати.

7.Запам'ятовування результатів.

8.Підготовка до виконання наступної команди, тобто обчислення її адреси.

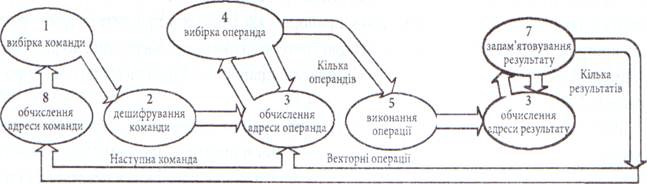

На рис. 3.2 показана діаграма циклу виконання команди, причому в нижній стрічці наведені операції, які виконуються всередині процесора, а в верхній стрічці - операції запису та вибірки із основної пам'яті. Операції 3 та 4 можуть повторюватись стільки разів, скільки потрібно вибрати операндів з основної пам'яті. Така ситуація відбувається при виконанні багатомісних операцій. Аналогічно можуть повторюватись операції 6 та 7, якщо отримано кілька результатів. При обробці декількох даних за однією командою операції 3-7 повторюються відповідну кількість разів. Такі операції називають векторними.

Рис. 3.2. Діаграма циклу виконання команди

3.1.3. Виконання команд на рівні регістрів процесора

Для глибшого розуміння послідовності виконання команди розглянемо детальніше структуру регістрової (надоперативної) пам'яті процесора. Ця пам'ять (рис. 3.3) складається з регістрів з закріпленими операціями, та регістрів зального призначення. Тут РгА, РгК і РгД - відповідно регістри адреси, команд і даних. РгА зберігає адресу даного або команди при зверненні до основної пам'яті. РгД зберігає операнд при його запису або зчитуванні з основної пам'яті. В ролі операнда може бути дане, команда або адреса. РгК зберігає команду після її зчитування з основної пам'яті. ПЛ - програмний лічильник, який підраховує команди та зберігає адресу поточної команди. Комп'ютер з архітектурою Джона фон Неймана має один програмний лічильник.

Рис. 3.3. Регістрова пам'ять процесора

Рис. 3.3. Регістрова пам'ять процесора

Більшість комп'ютерів мають в складі процесора тригери для зберігання бітів стану процесора, або, як їх іще називають, прапорців. Кожен прапорець має спеціальне призначення. Частина прапорців вказує на результати арифметичних і логічних операцій: додатній результат (Р), від'ємний результат (N), нульовий результат (Z), перенос (С), арифметичне переповнення (V), і т. д. В системі команд комп'ютера є команди, які вказують процесору коли встановити чи скинути ці тригери. Інша частина прапорців вказує режими захисту пам'яті. Існують також прапорці, які вказують пріоритети виконуваних програм. В деяких процесорах додаткові тригери служать для зберігання кодів умов, формуючи регістр кодів умов. Взяті разом описані прапорці формують слово стану програми (ССП), а відповідні тригери - регістр ССП.

Регістри загального призначення (РЗП) є програмно доступними. Зазвичай їх називають регістровим файлом. Вони можуть використовуватись програмістом в якості регістрів для зберігання вхідних та вихідних даних, а також проміжних результатів обчислень, в якості адресних та індексних регістрів при виконанні операцій модифікації адрес. Наприклад, в процесорі UltraSPARC II є дві групи регістрових файлів: 32 64-розрядні регістри загального призначення та 32 регістри для даних з рухомою комою, які можуть зберігати або 32-розрядні дані одинарної точності, або 64-розрядні дані подвійної точності. В процесорі Pentium II є лише 8 32-розрядних та 6 16-розрядних регістрів загального призначення.

Зв'язки між вузлами процесора і основною пам'яттю показано на рис. 3.4. Як видно з рисунка, процесор взаємодіє з основною пам'яттю через регістри адрес та даних. Крім того, пристрій керування формує сигнали задання режимів роботи пам'яті.

Рис. 3.4. Зв'язки між процесором і основною пам'яттю

Виходячи з наведеної вище інформації про вузли процесора та його зв'язки з основною пам'яттю, розглянемо детальніше виконання команд на прикладі виконання операції додавання слова, яке знаходиться в пам'яті за адресою 9, з вмістом регістра РгО регістрової пам'яті процесора, коли результат операції засилається в пам'ять за адресою 9. Програма обчислень знаходиться також в пам'яті. Операцію можна записати наступним чином:

[Комірка 9] := [Комірка 9] + [РгО].

Послідовність дій при виконанні цієї операції буде наступною:

1.Рг А := ПЛ. Значення із програмного лічильника, тобто адреса команди, записується в регістр адреси РгА.

2.Зчитування із комірки [РгА] основної пам'яті команди додавання двох чисел в регістр даних РгД.

3.Рг К := Рг Д. Перезапис команди додавання двох чисел з регістра даних в регістр команди РгК.

4.РгА := [А РгК]. Запис адреси числа із регістра команди до регістра адреси (ця адреса рівна 9).

5.Зчитування із комірки [РгА] основної пам'яті даного і засилання його в регістр РгД.

6.Рг Д := [РгД] + [Рг0]. Виконання в АЛП операції [РгД] + [Рг0] і засилання результату в РгД.

7.Запис в комірку 9 основної пам'яті даного із регістра РгД.

8.ПЛ := ПЛ +1. Прирощення на одиницю вмісту програмного лічильника.

Подібним чином виконуються інші команди, включаючи команди взаємодії з пристроями введення-виведення.

Дата добавления: 2014-12-23; просмотров: 616; Мы поможем в написании вашей работы!; Нарушение авторских прав |