КАТЕГОРИИ:

АстрономияБиологияГеографияДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРиторикаСоциологияСпортСтроительствоТехнологияФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Условное обозначение ЭСЛ приведено на рисунке 5.3

5.4 Логические элементы на МДП- транзисторах

а) схема инвертора на МДП приведена на рисунке 5.4.

Транзистор VT1 работает в ключевом режиме, VT2 – всегда в активном. VT2 является нелинейной нагрузкой.

Транзистор VT1 работает в ключевом режиме, VT2 – всегда в активном. VT2 является нелинейной нагрузкой.

При запертом VT1 транзистор VT2 ‑ в активном режиме, ближе к насыщению, при насыщенном VT1 транзистор VT2 – в активном, ближе к отсечке. При подаче на вход х низкого уровня напряжения VT1 запирается, VT2 близок к насыщению, на выходе ключа высокий уровень напряжения. При подаче на вход х высокого уровня напряжения VT1 отпирается, VT2 близок к отсечке, на выходе ключа низкий уровень напряжения. Выполняется операция  ;

;

б) в двухвходовой схеме ИЛИ-НЕ (рисунок 5.5) входные транзисторы VT1 и VT2 соединены параллельно. Если хотя бы на один из входов подан высокий уровень напряжения, соответствующий транзистор отпирается, и на выходе

б) в двухвходовой схеме ИЛИ-НЕ (рисунок 5.5) входные транзисторы VT1 и VT2 соединены параллельно. Если хотя бы на один из входов подан высокий уровень напряжения, соответствующий транзистор отпирается, и на выходе  схемы будет низкий уровень. И только при подаче на все входы схемы низкого уровня транзисторы VT1 и VT2 запрутся, и на выходе появится высокий уровень. Выполняется

схемы будет низкий уровень. И только при подаче на все входы схемы низкого уровня транзисторы VT1 и VT2 запрутся, и на выходе появится высокий уровень. Выполняется  ;

;

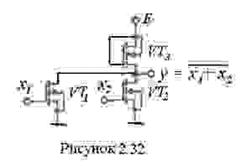

в) в двухвходовой схеме И-НЕ (рисунок 5.6) входные транзисторы VT1 и VT2 соединены последовательно. Если хотя бы на один из входов подан низкий уровень напряжения, соответствующий транзистор запирается, ток через входные транзисторы не течет, и на выходе схемы будет высокий уровень. И только при подаче на все входы схемы высокого уровня транзисторы VT1 и VT2 откроются, течет ток, и на выходе будет низкий уровень. Выполняется операция  .

.

Дата добавления: 2015-02-09; просмотров: 292; Мы поможем в написании вашей работы!; Нарушение авторских прав |