КАТЕГОРИИ:

АстрономияБиологияГеографияДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРиторикаСоциологияСпортСтроительствоТехнологияФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Последовательностные логические устройства

Кроме комбинационных устройств, рассмотренных в предыдущей главе, существует класс цифровых устройств, в которых при одинаковых воздействиях на входе, на выходе автомата могут возникать различные выходные состояния. Состояние выхода такого устройства зависит не только от того, какие сигналы присутствуют на его входах в данный момент времени, но и от того, какие последовательности сигналов поступали на входы устройства в предшествующие моменты времени, т.е. автомат помнит свою предысторию и хранит ее в памяти. Поэтому такие устройства называют последовательностными или дискретными автоматами с памятью.

Для описания последовательностного автомата с памятью, помимо состояний входов X(t) и выходов Y(t), необходимо также знать состояние памяти автомата, как говорят, его внутреннее состояние S(t). Функционирование (т.е. изменение состояния устройства) многотактного автомата происходит в дискретные моменты времени (такты), ход которого обозначается натуральными числами t = 1, 2, 3 и т.д.

В каждый момент дискретного времени t автомат находится в определенном состоянии S(t), воспринимает через входы соответствующую данному моменту комбинацию входных переменных X(t), выдает на выходах некоторую функцию выхода Y(t), определяемую как Y(t) = f (S(t), X(t)), и переключается в новое состояние S(t+1), которое определяется функцией переходов j как S(t + 1) = j (S(t), X(t)).

Закон функционирования последовательностных автоматов может задаваться в виде уравнений, таблиц и графов. Под законом функционирования понимается совокупность правил, описывающих последовательность переключения состояний автомата и последовательность выходных сигналов в зависимости от последовательности поступления входных сигналов.

В общем виде последовательностный автомат рассматривается состоящим из двух частей: комбинационного устройства и элементов памяти, каковыми обычно являются триггеры различных типов или схемы на их основе.

Триггер – это устройство, которое хранит 1 бит информации (простейший элемент памяти). Он имеет два состояния выхода: Q = 1 (  ); Q = 0 (

); Q = 0 (  ) и два режима: записи и хранения. Структурная схема любого триггера имеет вид, приведённый на рис. 3.26.

) и два режима: записи и хранения. Структурная схема любого триггера имеет вид, приведённый на рис. 3.26.

Рис. 3.26 Обобщённая схема триггера

Здесь: Тг – запоминающая ячейка (простейший R-S триггер); Т1-Тn – тактовые входы (чаще – только один), которые служат для блокировки входной информации. Если Т = 1, то входы принимают сигналы и воздействуют на состояние Тг, иначе – нет. Входы А1…Аn являются информационными. В зависимости от организации схемы управления состояние этих входов может по-разному влиять на состояние триггера.

Рис. 3.27 Классификация триггеров по способу управления

Все триггеры классифицируются по двум признакам: по способу управления и по характеру влияния сигналов управления на состояние триггера. По способу управления они делятся на асинхронные и синхронные. В первых из них тактовый вход T (см. рис. 3.26) отсутствует и их состояние изменяется сразу после изменения значений информационных входов (блокировка отсутствует). Синхронные триггеры подразделяются на универсальные и динамические. В первые из них запись разрешается уровнем тактового импульса (Т = 1 либо Т = 0). Если такое состояние тактового входа поддерживать постоянно, то такой триггер превращается в асинхронный. В динамических же запись разрешается перепадом импульса (фронтом либо срезом) и подачей на Т-вход любого логического уровня разрешить запись невозможно. Классификация триггеров по данным признакам приведена на рис. 3.27.

По характеру влияния сигналов управления на состояние триггеры делятся на RS, E, S, R, JK, T, D, DV и другие типы.

RS–триггер. Важным методом, используемым для описания функционирования триггеров, является метод таблиц состояний (таблиц переходов). Таблица состояний (рис. 3.28) RS-триггера в сокращенной форме (эту таблицу называют также управляющей таблицей, таблицей функционирования) содержит два входных сигнала (сигналы R и S) и один выходной сигнал Q (функция). Хотя триггеры имеют два выхода – один прямой Q, а другой – инверсный `Q, в описании триггера и в таблице состояний указывают лишь состояние прямого выхода Q.

Из таблицы состояний триггера видно, что при подаче на вход R уровня лог. «1» триггер принимает состояние логического «0», а при подаче управляющего сигнала «1» на вход S – состояние «1». Следует отметить также, что если до подачи управляющего сигнала, например, на вход R, триггер находился в состоянии логического «0», его состояние не изменится и после подачи сигнала «1» на вход R. Если на обоих входах триггера имеются уровни логического «0» – это состояние соответствует режиму хранения и триггер сохраняет предыдущее состояние. При подаче на входы R и S одновременно уровня «1» триггер будет находиться в неопределенном (или неправильном) состоянии, поэтому такое сочетание сигналов R и S называется запрещенной комбинацией управляющих сигналов и в таблице состояний обозначается символом ´.

Рис. 3.28 Таблица истинности RS-триггера

Сокращенная таблица состояний триггера (см. рис. 3.28) отражает лишь динамику изменения состояния триггера и не учитывает свойство триггера запоминать единицу информации. Полная таблица состояний триггера должна учитывать влияние (на процесс управления) значения предыдущего состояния триггера Qn. Причем Qn представляется как входная переменная.

Из рис. 3.28 следует:

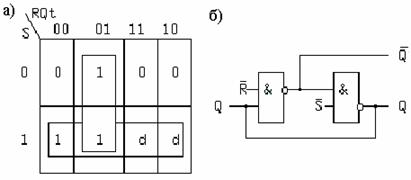

Последняя комбинация является запрещённой (избыточной), и её можно использовать для упрощения, которое приведено на рис. 3.29.

Рис. 3.29 Упрощение функции RS-триггера (а) и его реализация (б)

Из карты следует:

или, используя правило де Моргана,

.

.

По последнему выражению построена схема, приведённая на рис. 3.29, б.

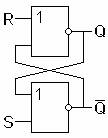

Обычно эту схему представляют в виде, показанном на рис. 3.30.

Так как полученный RS триггер имеет инверсные входы, то он управляется значениями входов, обратными приведённым на рис. 3.28, т.е. ввод значений будет производиться нулевыми логическими уровнями.

Рис. 3.30 RS-триггер в базисе И-НЕ

Рис. 3.31 RS-триггер в базисе ИЛИ-НЕ

Точно так же можно построить RS-триггер и на логических элементах "ИЛИ". Схема RS-триггера, построенного на логических элементах "ИЛИ", приведена на рис. 3.31. Единственное отличие будет заключаться в том, что сброс и установка триггера будет производиться единичными логическими уровнями. Условное обозначение RS-триггера приведены на рис. 3.32.

Рис. 3.32 Графическое обозначение

Рис. 3.33 Временная диаграмма работы R-S триггера

Временные диаграммы, поясняющие работу RS-триггера, приведены на рис. 3.33. Из временных диаграмм следует, что рассмотренные выше RS-триггеры опрокидываются, т.е. управляются сигналами R и S, в любой момент времени. В тех случаях, когда длительности управляющих сигналов не синхронизированы (не согласованы), триггер может находиться в неопределенном состоянии (интервалы времени t4, t5), и поэтому такие триггеры называют асинхронными.

Схема триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется гонками), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены. То есть цифровые схемы требуют синхросигнала. Все переходные процессы должны закончиться за время периода синхросигнала.

Для таких цифровых схем требуются синхронные триггеры. Синхронные триггеры снабжаются дополнительным входом, по которому поступает синхронизирующий (тактирующий) сигнал. При этом изменение состояния триггера происходит (при наличии управляющего сигнала) только в те моменты времени, когда на специальный синхровход триггера поступает тактирующий импульс. Синхронизирующий вход обозначается буквой С.

Схема синхронного триггера приведена на рис. 3.34, а, на рис 3.34, б приведено его обозначение на принципиальных схемах. На рис 3.35 приведена временная диаграмма его работы.

Рис. 3.34 Схема (а) и условное обозначение (б) синхронного RS-триггера

Рис. 3.35 Временные диаграммы работы синхронного RS-триггера

Двухступенчатый RS-триггер. Рассмотренные схемы RS-триггеров являются одноступенчатыми. Применение одноступенчатых RS-триггеров в качестве самостоятельных запоминающих элементов ограничено. Это связано с неустойчивой работой последовательностной схемы (цифрового автомата), память которой выполнена на одноступенчатых RS-триггерах.

Сигналы переключения триггера S(t), R(t) формируются в цифровом автомате комбинационной схемой, в их формировании участвуют, наряду с внешними логическими сигналами, сигналы с выходов Q(t) и  . Переключение одноступенчатого триггера под действием сигналов S(t) и R(t) вызывает изменение значений сигналов Q(t) и

. Переключение одноступенчатого триггера под действием сигналов S(t) и R(t) вызывает изменение значений сигналов Q(t) и  , а их изменение может привести к изменениям сигналов S(t) или R(t) в том же такте времени t и, как следствие, к ложному срабатыванию триггера. Для устойчивой работы триггера необходимо, чтобы сигналы Q(t) и

, а их изменение может привести к изменениям сигналов S(t) или R(t) в том же такте времени t и, как следствие, к ложному срабатыванию триггера. Для устойчивой работы триггера необходимо, чтобы сигналы Q(t) и  изменялись только после прекращения действия входного сигнала S(t) или R(t). Это требование выполняется в двухступенчатых триггерах (MS-триггерах). Базовыми схемами для построения двухступенчатых триггеров являются одноступенчатые RS-триггеры.

изменялись только после прекращения действия входного сигнала S(t) или R(t). Это требование выполняется в двухступенчатых триггерах (MS-триггерах). Базовыми схемами для построения двухступенчатых триггеров являются одноступенчатые RS-триггеры.

Двухступенчатый триггер состоит из двух секций (ступеней), соединенных каскадно, как показано на рис. 3.36, а, причем каждая секция содержит по синхронному RS-триггеру. Первая секция, ведущая или М-секция (М происходит от английского MASTER – хозяин), принимает информацию со входных линий S и R. Состояние выходов ведущей секции подается на вторую секцию, ведомую или S-секцию (S происходит от английского SLAVE – слуга).

Для ведущего триггера используется обычная синхронизация, в то время как для ведомого триггера импульс синхронизации инвертируется. Изменение состояния выхода ведущего триггера будет происходить в момент появления положительного импульса синхронизации, и эти изменения будут переданы на входы ведомого триггера. Однако никакие изменения на выходе ведомого триггера не будут происходить до тех пор, пока не появится положительный сигнал инвертированного импульса синхронизации, т.е. отрицательный (задний фронт) фронт исходного синхроимпульса. Следовательно, изменения на выходах не произойдет до тех пор, пока не завершится импульс синхронизации. На рис. 3.36, б показаны временные диаграммы работы триггера.

На функциональных схемах двухступенчатый триггер изображается в соответствии с рис. 3.36, в. Символ ТТ в поле условного обозначения означает, что триггер двухступенчатый.

D-триггер (от английского DELAY) называют информационным триггером, также триггером задержки. D-триггер бывает только синхронным. Он может управляться (переключаться) как уровнем тактирующего импульса, так и его фронтом. Для триггера типа D состояние в интервале времени между сигналом на входной линии и следующим состоянием триггера формируется проще, чем для любого другого типа.

Рис. 3.36. Двухступенчатый RS-триггер

По синхроимпульсу D-триггер принимает то состояние, которое имеет входная линия, согласно управляющей таблице состояний, приведенной на рис. 3.37, а. На рис. 3.37, б приведены временные диаграммы, поясняющие его работу.

Рис. 3.37 Таблица управления (а) и временные диаграммы (б) D-триггера

Как следует из управляющей таблицы, D-триггер имеет как минимум две входные линии: одна – для подачи синхроимпульсов; другая – информационных сигналов. Схемное обозначение D-триггера приведено на рис. 3.38.

Рис. 3.38 Устройство (а) и схемное обозначение (б) D-триггера

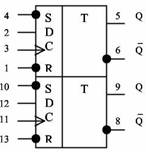

Рис. 3.39 Схемное обозначение ИМС К1533ТМ2

На рис. 3.39 приведено обозначение D-триггера К1533ТМ2, выпускаемого промышленностью в виде интегральной микросхемы (ИМС).

В одном корпусе ИМС содержится два D-триггера, управляемых фронтом. D-триггеры в интегральном исполнении имеют также дополнительные асинхронные входы управления S и R. Функции асинхронных входов не зависят от сигналов синхронизации. Отметим, что асинхронные входы имеют и другие типы триггеров. Поскольку дополнительные входы “предустановка” и “очистка”, с помощью которых триггер может быть установлен в нужное состояние независимо от сигналов на других входах, включая синхронизирующий, работают независимо от синхронизации, их называют асинхронными.

Входы “предустановки” и “очистки” напоминают соответствующие входы S и R обычного несинхронизируемого RS-триггера. При подаче “1” на вход R и “0”, на вход S (см. рис. 3.38) триггер устанавливается в состояние “0”. При подаче “1” на оба эти входа поведение триггера не определено, т.е. комбинация S = 1, R = 1 является запрещенной. При подаче на эти входы “1” поведение триггера полностью определяется другими входными сигналами и синхросигналом. Входы S и R необходимы, например, для установки триггеров в определённое состояние (чаще – «0») после подачи на схему напряжения питания, когда их состояние не определено.

Рис. 3.40 T-триггер: а – временная диаграмма работы; б – условное графическое обозначение; в – схема с четырмя ЛЭ И-НЕ

T-триггер. Триггер типа Т представляет собой устройство с двумя устойчивыми выходными состояниями, сменой которых управляют только по одному входу Т (рис. 3.40). Подача импульса на этот вход приводит к смене состояния триггера на противоположное. На выходе Q возникает уровень напряжения, бывший на  , и наоборот.

, и наоборот.

На рис. 3.40, в показана схема T-триггера в базисе И-НЕ. Когда Q = 1, состояние другого выхода  = 0. Так как вход А соединен с выходом

= 0. Так как вход А соединен с выходом  , то на входе А напряжение низкого уровня. После поступления входного импульса на вход Т на выходе элемента DD3 установится напряжение низкого уровня (Q = 0 и

, то на входе А напряжение низкого уровня. После поступления входного импульса на вход Т на выходе элемента DD3 установится напряжение низкого уровня (Q = 0 и  = 1). При поступлении следующего тактового импульса на входе А уже будет напряжение высокого уровня и произойдет новая смена состояния (см. рис. 3.40, a).

= 1). При поступлении следующего тактового импульса на входе А уже будет напряжение высокого уровня и произойдет новая смена состояния (см. рис. 3.40, a).

Состояние T-триггера меняется с поступлением на вход очередного импульса. Таблица состояний T-триггера имеет следующий вид (рис.3.41).

Рис. 3.41 Таблица состояния Т-триггера

JK-триггер. Среди триггеров особое место занимают JK-триггеры, имеющие более широкие функциональные возможности.

Упрощенная таблица (таблица управления) состояний JK-триггера содержит четыре строки (рис. 3.42, а).

Из таблицы состояний видно, что для первых трех строк (наборов переменных) входы J и K играют роль входов S и R RS-триггера. Однако для четвертого набора переменных, когда J = K = = 1 состояние триггера сильно отличается от состояния RS-триггера. Для RS-триггера – это запрещенная комбинация входных переменных, а в JK-триггере меняется (инвертируется) предыдущее состояние. JK-триггер можно синтезировать (построить) на базе двухступенчатого RS-триггера, для чего следует представить функциональную схему JK-триггера как совокупность КУ и синхронного RS-триггера (рис. 3.42, б).

Рис. 3.42 Упрощенная таблица состояний (а) и функциональная схема JK-триггера (б)

Для получения логических выражений (характеристических уравнений) функций R и S комбинационного устройства необходимо построить совмещенную таблицу состояний JK и RS-триггеров (рис. 3.43, а).

Из полученных выражений для S и R (рис. 3.43, б) следует, что для построения JK-триггера из двухступенчатого RS-триггера потребуется два элемента конъюнкции (на два входа каждый).

Рис. 3.43 Таблица состояний (а) и карты Карно JK-триггера (б)

Схема, полученная путем синтеза JK-триггера, приведена на рис. 3.44, а. Обозначение JK-триггера на функциональных схемах приведено на рис. 3.44, б.

Выпускаемые промышленностью ИМС JK-триггеры могут иметь несколько входов (до трех) J и такое же количество входов K, объединенных схемами конъюнкций.

Рис. 3.44 Синтезируемая схема (а) и графическое обозначение (б) JK – триггера

Регистры. Наиболее распространенным узлом цифровой техники и устройств автоматики являются регистры. Регистры строятся на базе синхронных одно- и двухступенчатых RS и D-триггеров. Регистры могут быть реализованы также на базе JK-триггеров. По способу приема и выдачи информации регистры делятся на следующие группы: с параллельным приемом и выдачей (рис. 3.45, а); с последовательным приемом и выдачей (рис. 3.45, б); с последовательным приемом и параллельной выдачей (рис. 3.45, в); с параллельным приемом и последовательной выдачей (рис. 3.45, г); комбинированные, с различными способами приема и выдачи (рис. 3.45, д) и реверсивные.

Рис. 3.45 Функциональные схемы основных типов регистров

Регистры хранения (пямяти). Регистры с параллельным приемом и выдачей информации служат для хранения информации и называются регистрами памяти или хранения. Изменение хранящейся информации в регистре памяти (запись новой информации) осуществляется после установки на входах D0…Dm новой цифровой комбинации (информации) при поступлении определенного уровня или фронта синхросигнала (синхроимпульса) С на вход “С” регистра.

Количество разрядов записываемой цифровой информации определяется разрядностью регистра, а разрядность регистра, в свою очередь, определяется количеством триггеров, образующих этот регистр. В качестве разрядных триггеров регистра памяти используются синхронизируемые уровнем или фронтом триггеры. Регистры памяти могут быть реализованы на D-триггерах, если информация поступает на входы регистра в виде однофазных сигналов, и на RS-триггерах, если информация поступает в виде парафазных сигналов. В некоторых случаях регистры могут иметь вход для установки выходов в состояние “0”. Этот асинхронный вход называют входом R “сброса” триггеров регистра. На рис. 3.46 приведены схемы четырехразрядных регистров памяти на D- и RS-триггерах, синхронизируемых уровнем и фронтом синхроимпульсов (обычно четыре триггера объединены в одном корпусе ИМС).

Регистры сдвига. Регистры с последовательным приемом или выдачей информации называются сдвиговыми регистрами или регистрами сдвига. Регистры сдвига могут выполнять функции хранения и преобразования информации. Они могут быть использованы для построения умножителей и делителей чисел двоичной системы счисления, т.к. сдвиг двоичного числа влево на один разряд соответствует умножению его на два, а сдвиг вправо – делению на два.

Рис. 3.46 Регистры хранения на D-триггерах, синхронизируемых

уровнем синхроимпульса (а), фронтом (б) и на RS-триггерах,

синхронизируемых фронтом (в)

Регистры сдвига широко используются для выполнения различных временных преобразований цифровой информации: последовательное накопление последовательной цифровой информации с последующей одновременной выдачей (преобразование последовательной цифровой информации в параллельный код) или одновременный прием (параллельный прием) информации с последующей последовательной выдачей (преобразование параллельного кода в последовательный). Регистры сдвига могут служить также в качестве элементов задержки сигнала, представленного в цифровой форме. Действительно, регистры с последовательным приемом (вводом) и выводом осуществляют задержку передачи информации на m + 1 тактов (m + 1 – число разрядов регистра) машинного времени. Регистры сдвига обычно реализуются на D-триггерах (рис. 3.47, а) или на RS-триггерах (рис. 3.47, б), где для ввода информации в первый разряд включается инвертор (первый разряд представляет собой D-триггер).

Рис. 3.47 Регистры сдвига на D-триггерах (а),

RS-триггерах (б) и комбинированный регистр на D-триггерах (в)

Рис. 3.48 Временные диаграммы, поясняющие работу регистра сдвига

Следует отметить, что все регистры сдвига строятся на базе двухступенчатых триггеров или синхронизируемых фронтом синхроимпульса. Разрядность регистров сдвига, как и у регистров хранения, определяется количеством триггеров, входящих в их состав. На рис. 3.47 приведены схемы четырехразрядных регистров сдвига, реализованных на D- и RS-триггерах, а временные диаграммы, поясняющие работу регистра сдвига, приведены на рис. 3.48.

Вывод параллельной информации из регистра сдвига (см. рис. 3.47, в) осуществляется при подключении всех триггеров регистра к отдельным выводам (см. на рис. 3.47, а и б эти выводы показаны штриховыми линиями). Как было сказано выше, регистры сдвига синхронизируются фронтом тактирующих импульсов, т.е. запись новой информации в триггеры регистра происходит в течение очень короткого времени – за время длительности фронта синхроимпульса, вернее в момент поступления соответствующего фронта синхроимпульса. Обычно это “время” значительно меньше времени распространения сигнала, т.е. времени переключения триггера регистра в новое состояние. Работу регистра сдвига рассмотрим на примере схемы, приведенной на рис. 3.47, а.

Можно предположить, что в начале все триггеры регистра находятся в состоянии логического нуля, т.е. Q0 = 0, Q1 = 0, Q2 = 0, Q3 = 0. Если на входе D-триггера Т1 имеет место логический 0, то поступление синхроимпульсов на входы “С” триггеров не меняет их состояния.

Как следует из рис. 3.47, синхроимпульсы поступают на соответствующие входы всех триггеров регистра одновременно и записывают в них то, что имеет место на их информационных входах. На информационных входах триггеров Т2, Т3, Т4 – уровни логического “0”, т.к. информационные входы последующих триггеров соединены с выходами предыдущих триггеров, находящихся в состоянии логического “0”, а на вход “D” первого триггера, по условию примера подается “0” из внешнего источника информации. При подаче на вход “D” первого триггера “1”, с приходом первого синхроимпульса в этот триггер запишется “1”, а в остальные триггеры – “0”, т.к. к моменту поступления фронта синхроимпульса на выходе триггера Т1 “ещё” присутствовал логический “0”. Таким образом, в триггер Т1 записывается та информация (тот бит), которая была на его входе “D” в момент поступления фронта синхроимпульса и т.д.

При поступлении второго синхроимпульса логическая “1”, с выхода первого триггера, запишется во второй триггер, и в результате происходит сдвиг первоначально записанной “1” с триггера Т1 в триггер Т2, из триггера Т2 в триггер Т3 и т.д. (см. рис. 3.48). Таким образом, производится последовательный сдвиг поступающей на вход регистра информации (в последовательном коде) на один разряд вправо в каждом такте синхроимпульсов.

После поступления m синхроимпульсов (на рис. 3.47 и рис. 3.48 m = 4) регистр оказывается полностью заполненным разрядами числа, вводимого через последовательный ввод “D”. В течение следующих четырех синхроимпульсов производится последовательный поразрядный вывод из регистра записанного числа, после чего регистр оказывается полностью очищенным (регистр окажется полностью очищенным только при условии подачи на его вход уровня “0” в режиме вывода записанного числа).

Кольцевые счетчики. На базе регистров сдвига можно построить кольцевые счетчики – счетчики Джонсона. Счетчик Джонсона имеет коэффициент пересчета вдвое больший числа составляющих его триггеров. В частности, если счетчик состоит из трех триггеров (m = 3), то он будет иметь шесть устойчивых состояний. Счетчик Джонсона используется в системах автоматики в качестве распределителей импульсов и т.д.

Таблица состояний счетчика Джонсона (рис. 3.49) содержит 2m строк и

m-столбцов (m – количество триггеров в составе регистра). Количество разрядов счетчика определяется количеством триггеров (см. рис. 3.49). Рассмотрим схему трехразрядного счетчика Джонсона, выполненного на базе D-триггеров (регистр сдвига реализован на D-триггерах). Для построения кольцевого счетчика достаточно соединить инверсный выход последнего триггера регистра (последнего разряда) с входом “D” (с входом, предназначенным для ввода последовательной информации) первого триггера.

Рис. 3.49 Таблица состояний (а) и схема (б) счетчика Джонсона

на трехразрядном регистре сдвига

Предположим, что вначале все триггеры находятся в состоянии “0”, т.е. Q0 = Q1 = = Q2 = 0. При этом на входе “D” первого триггера присутствует уровень “1”, т.к  = 1. Первым синхроимпульсом в триггер Т1 запишется “1”, вторым - единица запишется в первый триггер, из первого – во второй и т.д. до тех пор, пока на всех выходах регистра не будет “1”. После заполнения регистра единицами на инверсном выходе триггера Т3 появится

= 1. Первым синхроимпульсом в триггер Т1 запишется “1”, вторым - единица запишется в первый триггер, из первого – во второй и т.д. до тех пор, пока на всех выходах регистра не будет “1”. После заполнения регистра единицами на инверсном выходе триггера Т3 появится  = 0 и четвертым синхроимпульсом в Т1 запишется логический “0” (см. рис. 3.48, б).

= 0 и четвертым синхроимпульсом в Т1 запишется логический “0” (см. рис. 3.48, б).

После поступления последующих трех синхроимпульсов регистр обнуляется и на его вход “D” снова подается уровень “1”. Таким образом, цикл повторения состояния кольцевого счетчика состоит из шести тактов синхросигнала. Как видим, при работе в начале от первого триггера до последнего триггера распространяется “волна единиц”, а затем “волна нулей”.

Счетчики и делители частоты. На базе счетных триггеров можно построить цифровое устройство, получившее название счетчика. Счетчики позволяют вести подсчет электрических импульсов, количество которых (поступивших на вход счетчика) представляется обычно в параллельном коде. Счетчики могут отличаться модулем счета и типом счетной последовательности, которая, в частности, может быть двоичной, двоично-десятичной, в коде Грея и т.п. Цифровые последовательностные устройства, выполненные по схеме счетчика, но имеющие один счетный вход и один выход называются делителями частоты. Таким образом, любой счетчик может служить в качестве делителя частоты, если используется информация только одного из его выходов. Так как счетчики и делители имеют единую структуру, основное внимание будет уделено синтезу счетчиков.

Счетчики и делители подразделяются на асинхронные и синхронные. У синхронных счетчиков все разрядные триггеры синхронизируются параллельно одними и теми же синхроимпульсами, поступающими из источника этих импульсов. Асинхронные счетчики имеют последовательную синхронизацию, т.е. каждый последующий разрядный триггер синхронизируется выходными импульсами триггера предыдущего разряда. Асинхронные счетчики иногда называют последовательными, а синхронные счетчики – параллельными.

Синхронные счетчики, в свою очередь, подразделяются на параллельно-синхронные и последовательно-синхронные. Параллельные счетчики имеют более высокую скорость счета, чем асинхронные.

Счетчики, независимо от способа синхронизации, подразделяются на счетчики прямого счета (суммирующие) и на счетчики обратного счета (вычитающие). В интегральном исполнении выпускаются также реверсивные счетчики, в которых имеется специальный вход для переключения режима работы, т.е. направления счета. Многие типы счетчиков, выпускаемые промышленностью в интегральном исполнении, имеют дополнительные входы предустановки, позволяющие использовать эти счетчики в режиме регистра памяти.

В качестве разрядных триггеров счетчиков и делителей могут быть использованы двухступенчатые D-триггеры, Т- и JK-триггеры.

Счетчики относятся к последовательностным устройствам с циклически повторяющейся последовательностью состояний. Число, соответствующее количеству импульсов (поступивших на вход счетчика), при котором счетчик “возвращается” в исходное состояние, называется модулемили коэффициентом счета. Модуль счета обычно обозначают буквой М(или Ксч). Например, максимальный модуль счета счетчика из двух триггеров равен М = 22 = 4, трех триггеров – М = 23 = 8 и т.д. В общем случае для n-разрядного счетчика – М = 2n. Модуль счета счетчика численно совпадает с модулем деления делителя частоты. Счетчик по модулю 8 позволяет реализовать (без дополнительных схемных затрат) делитель частоты на 8. Это значит, что данный делитель делит частоту входной импульсной последовательности на 8.

Асинхронный двоичный счетчик. Асинхронный двоичный счетчик представляет собой совокупность последовательно соединенных триггеров (D- или JK), каждый из которых ассоциируется с битом в двоичном представлении числа. Если в счетчикеm триггеров, то число возможных состояний счетчика равно 2m, и, следовательно, модуль счета М также равен 2m. Счетная последовательность в двоичном суммирующем счетчике начинается с нуля и доходит до максимального числа 2m - 1, после чего снова проходит через нуль и повторяется. В вычитающем двоичном счетчике последовательные двоичные числа перебираются в обратном порядке, и при повторении последовательности максимальное число следует за нулем.

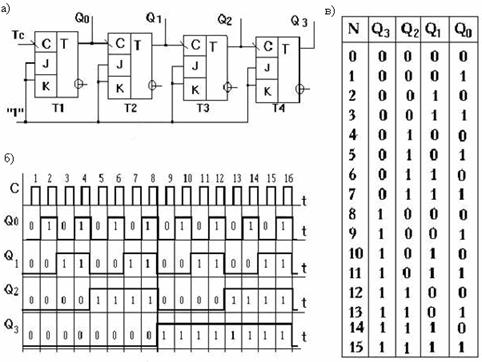

Рассмотрим устройство двоичного суммирующего счетчика по модулю М = 16, выполненного на базе JK-триггеров (рис. 3.50, а).

Как видно из рис. 3.50, а синхронизирующие входы всех триггеров, кроме крайнего левого (Т1), соединены с выходами предыдущих триггеров. Поэтому состояние триггера меняется в ответ на изменение состояния предыдущего триггера.

Из таблицы состояния счетчика (см. 3.50, б) легко заметить, что значение разряда в выбранной позиции меняется тогда, когда в соседней справа позиции состояние переходит из “1” в “0”, управление триггерами осуществляется задним фронтом синхроимпульсов (отрицательным перепадом напряжения импульса синхронизации).

Временные диаграммы, поясняющие работу асинхронного суммирующего счетчика приведены на рис. 3.50, в.

Счетчики обратного счета(вычитающие счетчики). На рис. 3.51 приведена схема асинхронного трехразрядного двоичного вычитающего счетчика, построенного на базе D-триггеров. Отметим, что условия для изменения состояний триггеров вычитающих счетчиков аналогичны условиям для суммирующих счетчиков с той лишь разницей, что они должны “опираться” на значения инверсных, а не прямых выходов триггеров. Следовательно, рассмотренный выше счетчик можно превратить в вычитающий, просто переключив входы “С” триггеров с выходов Q на выходы  . Когда в качестве разрядных триггеров используются D-триггеры, синхронизируемые передним фронтом синхроимпульсов, для получения вычитающего счетчика (асинхронного) входы “С” последующих тригеров соединяются с прямыми выходами предыдущих так же, как в счетчике прямого счета, построенного на JK-триггерах.

. Когда в качестве разрядных триггеров используются D-триггеры, синхронизируемые передним фронтом синхроимпульсов, для получения вычитающего счетчика (асинхронного) входы “С” последующих тригеров соединяются с прямыми выходами предыдущих так же, как в счетчике прямого счета, построенного на JK-триггерах.

Рис. 3.50 Схема (а) таблица состояний триггеров (б) и временные диаграммы, поясняющие работу (в) последовательного четырехразрядного счетчика на JK-триггерах

Работа вычитающего счетчика на D-триггерах наглядно иллюстрирована на

рис. 3.51, б. Из рис. 3.51 следует, что после нулевого состояния всех триггеров, с приходом первого синхроимпульса они устанавливаются в состояние “1”.

Поступление второго синхроимпульса приводит к уменьшению этого числа на одну единицу и т.д. После поступления восьмого импульса снова все триггеры обнуляются и цикл счета повторяется, что соответствует модулю М = 8.

Рис. 3.51 Схема (а) и временные диаграммы

трехразрядного счетчика на D-триггерах (б)

В некоторых случаях необходимо, чтобы счетчик мог работать как в прямом, так и в обратном направлении счета. Такие счетчики называются реверсивными. Реверсивные счетчики могут быть как асинхронного, так и синхронного типа. Они строятся путем применения логических коммутаторов (мультиплексоров) в цепях связи между триггерами. Так, например, асинхронный реверсивный двоичный счетчик можно построить, если обеспечить подачу сигналов с прямого (при суммировании) или с инверсного (при вычитании) выхода предыдущего JK- или Т-триггера на счетный вход последующего. В случае, когда реверсивный счетчик строится на базе D-триггеров, управляемых передним фронтом, для получения режима прямого счета следует соединить инверсный выход предыдущего с счетным входом последующего триггера.

Все рассмотренные типы счетчиков могут быть использованы в цифровых устройствах “умеренного” быстродействия, когда частота следования синхроимпульсов не превышает критического значения, при котором время задержки установки триггеров последних (старших) разрядов счетчика становится соизмеримым с длительностью периода входных тактовых импульсов. В связи с этим, асинхронные счетчики строятся на относительно небольшое количество разрядов, так как при большем количестве разрядов выходные сигналы триггеров старших разрядов появляются позднее, чем управляющие фронты синхроимпульсов (поступающих на вход первого триггера).

Параллельные счетчики (синхронные счетчики). Как было уже сказано выше, параллельные счетчики бывают двух типов: синхронные параллельные и синхронные последовательные.

Синхронный последовательный счетчик. По способу подачи синхроимпульсов такие счетчики параллельные, т.е. синхроимпульсы поступают на все триггеры счетчика параллельно, а по способу управления (подачи управляющих импульсов) – последовательные. Схема синхронного последовательного счетчика, реализованного на JK-триггерах, приведена на рис. 3.52.

Рис. 3.52 Синхронный последовательный счетчик на JK-триггерах

Синхронный последовательный счетчик обладает повышенным быстродействием, однако за счет последовательного формирования управляющих уровней, на входы “J” и “К” счетных триггеров быстродействие несколько уменьшается. От этого недостатка лишены параллельные синхронные счетчики, в которых формирование управляющих уровней и их подача на соответствующие входы триггеров счетчика осуществляется одновременно, т.е. параллельно. Пример реализации параллельного синхронного счетчика иллюстрирован на рис. 3.53.

Поскольку счетчик имеет одну общую линию синхронизации, состояние триггеров меняется синхронно, т.е. те триггеры, которые по синхроимпульсу должны изменить свое состояние, делают это одновременно, что существенно повышает быстродействие синхронных счетчиков.

Рис. 3.53 Параллельный синхронный счетчик на JK-триггерах

Счетчики с произвольным коэффициентом счета. Принцип построения подобного класса счетных устройств состоит в исключении нескольких состояний обычного двоичного счетчика, являющихся избыточными для счетчиков с коэффициентом пересчета, отличающимися от двоичных. При этом избыточные состояния исключаются с помощью обратных связей внутри счетчика.

Число избыточных состояний для любого счетчика определяется из следующего выражения:

М = 2m – Ксч,

где М – число запрещенных состояний, 2m – число устойчивых состояний двоичного счетчика; Ксч – требуемый коэффициент счета.

Задача синтеза счетчика с произвольным коэффициентом счета заключается в определении необходимых обратных связей и минимизации их числа. Требуемое количество триггеров определяется из выражения

n = [log2 Ксч],

где [log2 Ксч] – двоичный логарифм заданного коэффициента пересчета Ксч, округленный до ближайшего целого числа.

В каждом отдельном случае приходится применять какие-то конкретные методы получения требуемого коэффициента пересчета. Существует несколько методов получения счетчиков с заданным коэффициентом пересчета Ксч. Один их этих методов заключается в немедленном сбросе в “0” счетчика, установившегося в комбинацию, соответствующему числу Ксч. Его называют также методом автосброса. Рассмотрим пример реализации счетчика с Ксч = 10 методом автосброса. Очевидно, что “сбрасывая” двоичный четырехразрядный счетчик на нуль каждый раз, когда он будет принимать состояние 1010, можно обеспечить ”возврат” счетчика в исходное состояние после каждых десяти импульсов. Подобный прием удобно применять при использовании счетчиков в интегральном исполнении, имеющих ячейки конъюнкции (И) на входах установки в нуль, как это сделано в микросхеме К1533ИЕ5. В данном примере (рис. 3.54) организованы соединения, обеспечивающие коэффициент пересчета Ксч = 10.

Как следует из рис. 3.54, роль ячейки, выявляющей факт достижения кодовой комбинации 1010 на выходах счетчика, играет ячейка И, уже имеющаяся на входе сброса ИМС К1533ИЕ5.

На рис 3.54 поясняются конфигурации соединений для получения различных коэффициентов пересчета с помощью счетчика К1533ИЕ5. Наиболее очевидные варианты получения коэффициентов (2, 4, 8, 16) в таблице не указаны.

Рис. 3.54 Пример реализации счетчика с Ксч = 10

В графе “Соединения” таблицы указано, какие выводы микросхемы должны быть соединены между собой, например, указание 1-12 означает, что нужно соединить вывод 1 с выводом 12. В строках “Ввод” и “Выход” таблицы указаны номера выводов микросхемы, на которые следует подавать входные импульсы и с которых надлежит снимать выходные соответственно. Следует отметить, что ИМС К1533ИЕ5 состоит из четырех счетных триггеров, один из которых имеет раздельные выводы входа и выхода, а остальные три триггера соединены последовательно по схеме асинхронного счетчика.

Синтез счетчика с произвольным коэффициентом счета. Один из методов проектирования счетчиков с заданным коэффициентом счета заключается в построении таблицы переходов, в первых столбцах которых будут отражены текущие состояния триггеров счетчика, а в последующих - следующие за ними состояния. Анализ таблицы позволяет установить те переходы, которые должны быть “сделаны” триггерами, входящими в состав счетчика. Затем с помощью управляющей таблицы соответствующего триггера находятся значения логических функций на управляющих входах триггеров, позволяющие осуществить эти переходы.

Рассмотрим пример синтеза синхронного двоично-десятичного счетчика на базе JK-триггеров. В табл. 3.6 приведена последовательность переходов десятичного счетчика.

В правой части табл. 3.6 приведены значения входных сигналов четырех триггеров. Для поиска этих значений должны быть проанализированы реализованные переходы, а затем с помощью управляющей таблицы определены соответствующие значения “J” и “K” входов триггеров.

Таблица 3.6

Таблица переходов счетчиков

На рис.3.55 приведены карты Карно для логических функций, которым должны соответствовать сигналы, присутствующие на управляющих входах триггеров (нулевые значения функций в клетки карты Карно не записаны).

После упрощения с помощью карт Карно полученные логические выражения, используемые для управления входами “J” и “К”, выглядят:

J4 = Q1 Q2 Q3; K4 = Q1;

J3 = Q1 Q2; K3 = Q1 Q2;

J2 =  ; K2 = Q1.

; K2 = Q1.

Просмотр столбцов J1 и К1 в табл. 3.6 показывает, что все значения либо “~“, либо “1”.

Рис. 3.55 Карты Карно для функции комбинационной логики

двоично-десятичного счетчика

Так как безразличные состояния могут также участвовать в процессе упрощения, то все клетки карты Карно для J1 и К1 оказываются заполненными символами “~“, “1” и “a“. Следовательно,

J1 = K1 = 1.

На рис. 3.56 показана схема двоично-десятичного синхронного счетчика.

Рис. 3.56 Схема реализации двоично-десятичного синхронного счетчика

Рис. 3.57 Временные диаграммы двоично-десятичного синхронного счетчика

на JK-триггерах

Временные диаграммы счетчика (см. рис. 3.56), заданного табл. 3.6, приведены на рис. 3.57.

Из рис. 3.57 следует, что все изменения состояний триггеров происходят во время формирования заднего фронта положительного импульса синхронизации. На временных диаграммах выходов Q1...Q4 присутствуют двоичные цифры, характеризующие текущее состояние счетчика.

Дата добавления: 2015-04-16; просмотров: 1217; Мы поможем в написании вашей работы!; Нарушение авторских прав |